【

儀表網 研發快訊】2026年1月29日,北京大學化學與分子工程學院彭海琳教授研究團隊在《科學》(Science)在線發表了題為《晶圓級超薄且均勻的范德華鐵電氧化物》“Wafer-scale ultrathin and uniform van der Waals ferroelectric oxide”的研究長文(Science 2026,391,eadz1655),報道了一種新型高介電常數(κ)范德華鐵電材料α-硒酸鉍(Bi2SeO5),首次在晶圓級尺度上實現了超薄、均勻鐵電薄膜及其異質結構的可控制備,并構筑了工作電壓超低(0.8V)、耐久性極高(可循環1.5×1012次以上)的高速鐵電晶體管,其綜合性能顯著超越了現有工業級鉿基鐵電體系,是目前已知工作電壓最小、能耗最低且耐久性最優的鐵電晶體管。進一步地,成功構建了可在CMOS兼容低電壓(<1V)下動態重構的存內邏輯運算電路。該工作在國際上首次展示了高性能晶圓級二維鐵電材料體系,為開發高能效先進芯片提供了突破性的材料基礎與可行技術路徑,有望推動人工智能硬件向更高算力、更低功耗的方向持續發展。

在人工智能(AI)時代,對高算力與低能耗芯片的需求日益迫切。傳統馮·諾依曼計算架構因存儲與計算單元分離,導致數據傳輸延遲大、能耗高,使芯片發展長期受限于“功耗墻”與“存儲墻”。為此,具有快速翻轉極化特性的非易失性鐵電材料,為發展存算一體架構提供了機遇。其中,鐵電場效應晶體管兼具邏輯與存儲功能,被視為構建下一代高能效嵌入式存儲器與存算一體芯片的核心器件。然而,其實用化面臨一項關鍵挑戰:必須在晶圓級制備出均勻、穩定超薄鐵電薄膜。當薄膜厚度減薄5納米乃至原子層級時,傳統鐵電材料的自發極化會顯著退化,界面去極化效應亦隨之加劇,導致器件性能嚴重下降。因此,如何在原子級厚度下保持鐵電特性并實現可靠、一致的晶圓級集成,已成為研制高能效鐵電存算一體芯片必須攻克的核心難題。

聚焦產業前沿瓶頸:高品質鐵電材料的制備困境

隨著AI、云計算、大數據和5G等技術的快速發展,對芯片性能的要求持續攀升。沿用數十年的馮·諾依曼架構因計算與存儲分離,嚴重制約系統能效的提升。鐵電材料憑借“自發極化”特性,被視為突破傳統架構、構建下一代存算一體芯片的關鍵所在。鐵電晶體管(FeFET)巧妙地將存儲與計算功能融合于單一器件,為晶體管賦予“記憶”能力,從根本上消除數據頻繁搬運帶來的能耗與延遲,尤其適用于存算一體及神經形態計算等先進架構。

然而,要實現與先進制程兼容的實際應用,仍需突破關鍵瓶頸:高品質鐵電超薄膜的均勻可控制備。當前主流的鉿基鐵電材料雖與硅工藝兼容,但在晶圓級、超薄化制備時,仍面臨均勻性不足與鐵電性衰退等問題。因此,亟需發展兼具晶圓級均勻性、超薄穩定鐵電性,且與半導體產線高度兼容的新型鐵電材料,以真正釋放存算一體芯片的潛力,推動其從實驗室走向規模化應用。

視頻:晶圓級超薄均勻鐵電薄膜α-Bi2SeO5及鐵電晶體管

深耕關鍵材料創新:新型鉍基二維高κ鐵電氧化物體系

為突破傳統芯片架構“功耗墻”和“存儲墻”制約,彭海琳課題組一直致力于探索適用于后摩爾時代非馮·諾依曼架構先進芯片的新材料體系。早在2018年,課題組便率先發現鉍基二維半導體Bi2O2Se的原生氧化物α-Bi2SeO5,并通過理論計算預測其具有鐵電性。但從理論到驗證是一條漫漫長路。受限于材料、器件與表征等多重瓶頸,該推測遲遲未能獲得實驗支撐。

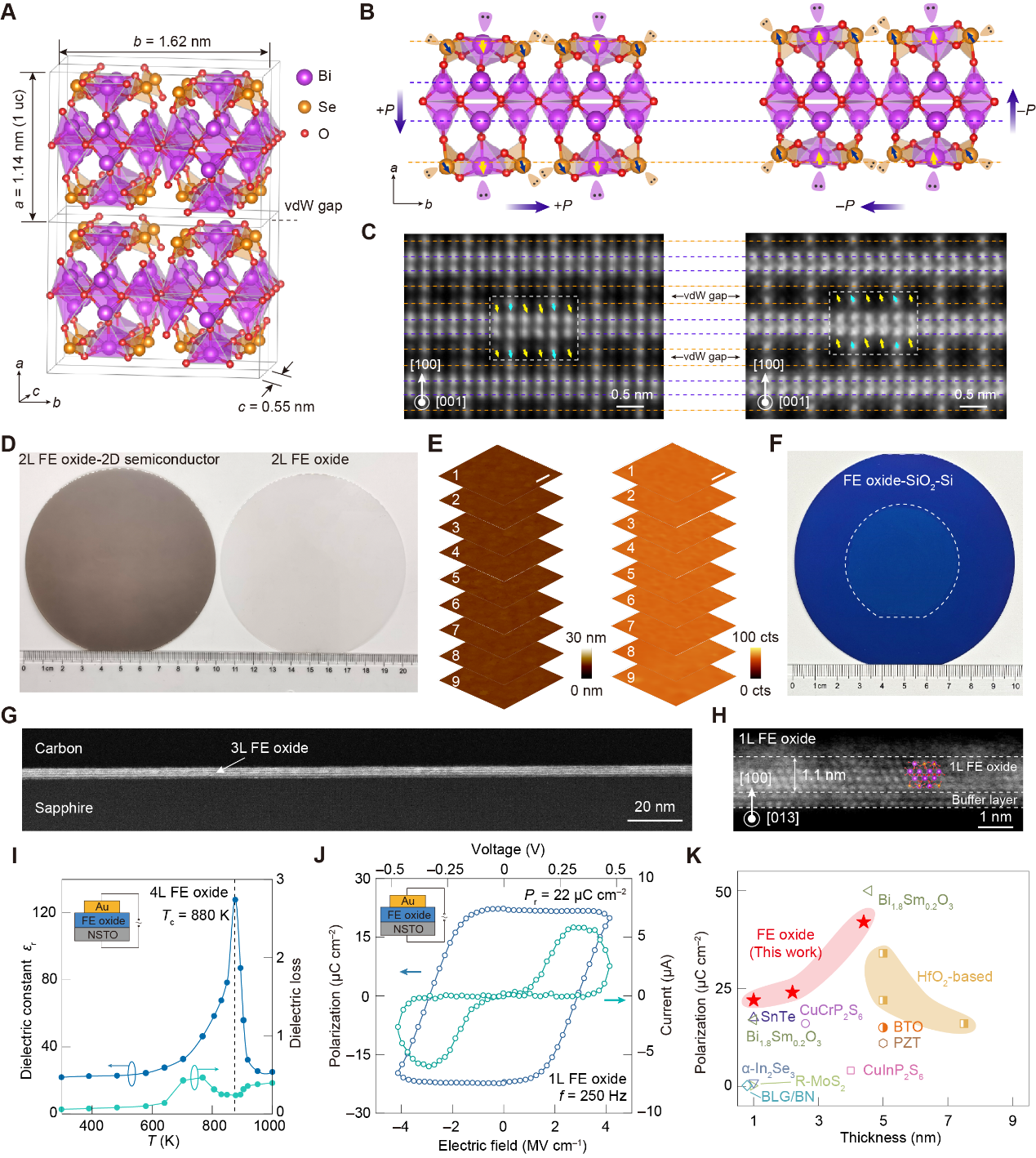

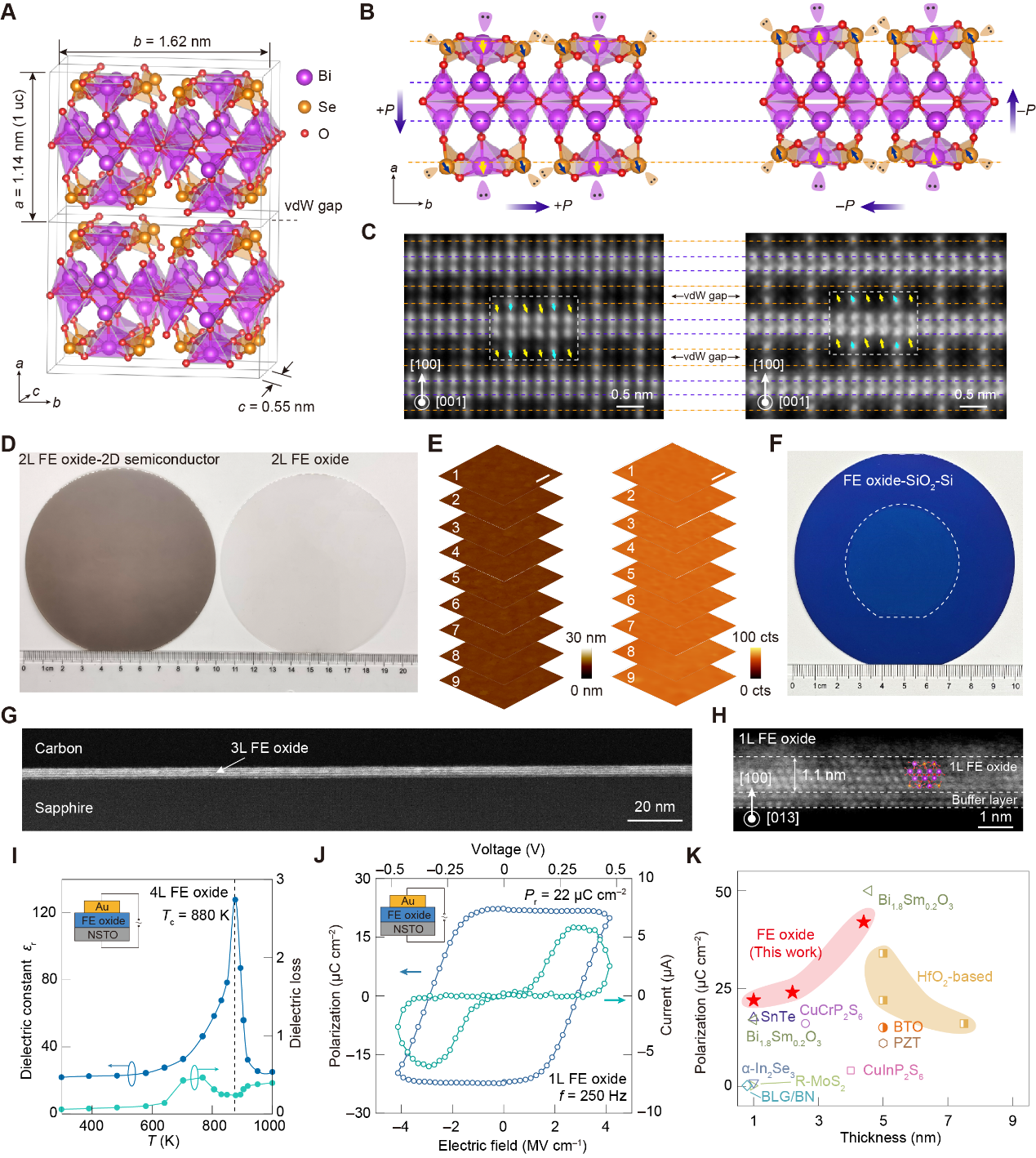

經過近8年的不懈探索,課題組終于首次在實驗上確證了α-Bi2SeO5的鐵電性,更建立了一套后道工藝兼容(≤400°C)的原位氧化制備方法,實現了超薄鐵電薄膜的晶圓級均勻制備(圖1)。憑借獨特的范德華層狀結構,α-Bi2SeO5即使薄至單層仍能保持穩定鐵電性,成為實現原子級厚度非易失存儲器及亞5納米三維存算一體架構的理想材料,為突破現有芯片性能邊界打開了全新可能。

圖2. 二維高 κ 鐵電氧化物α-Bi2SeO5的晶圓級均勻制備及鐵電性

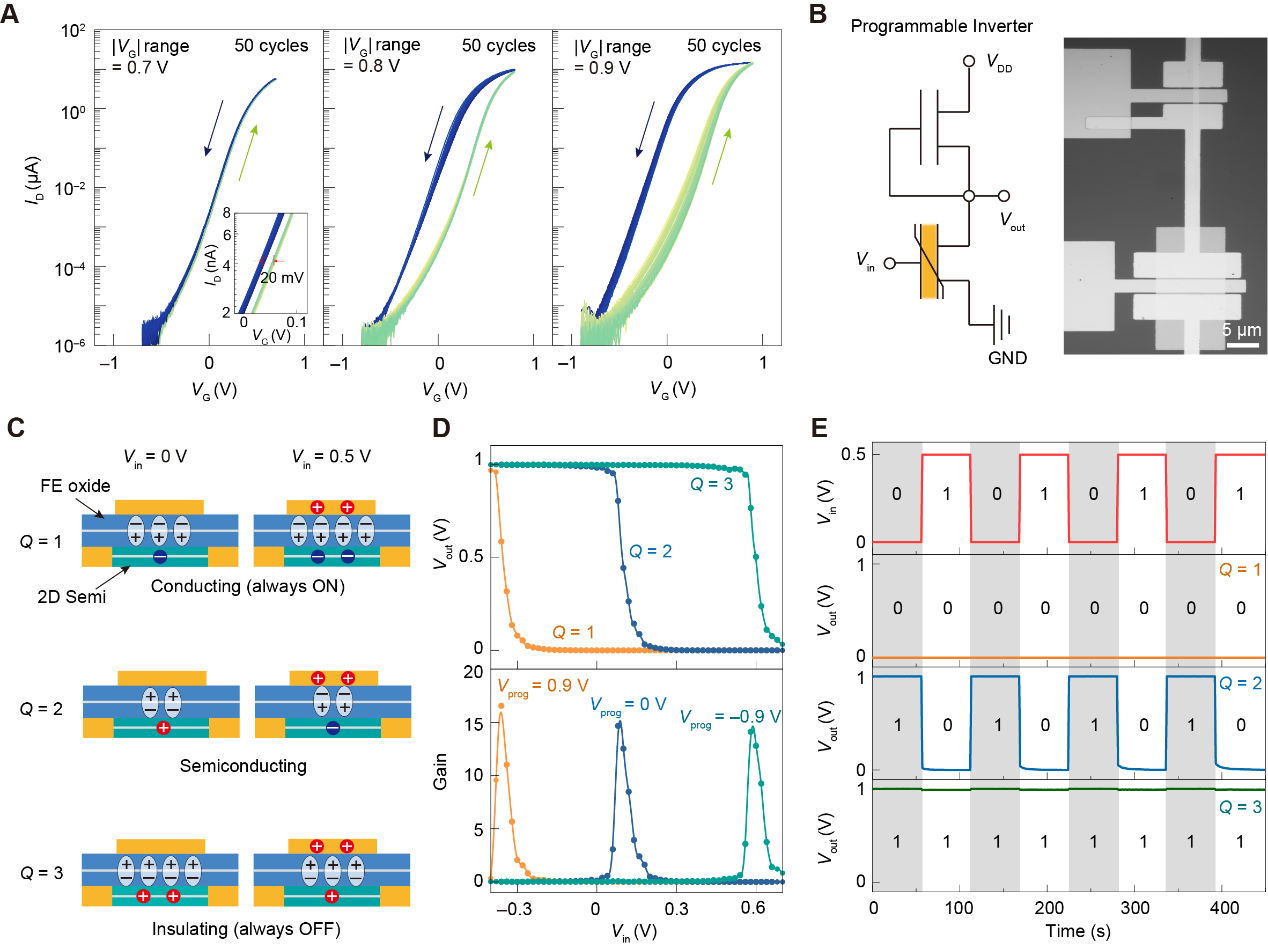

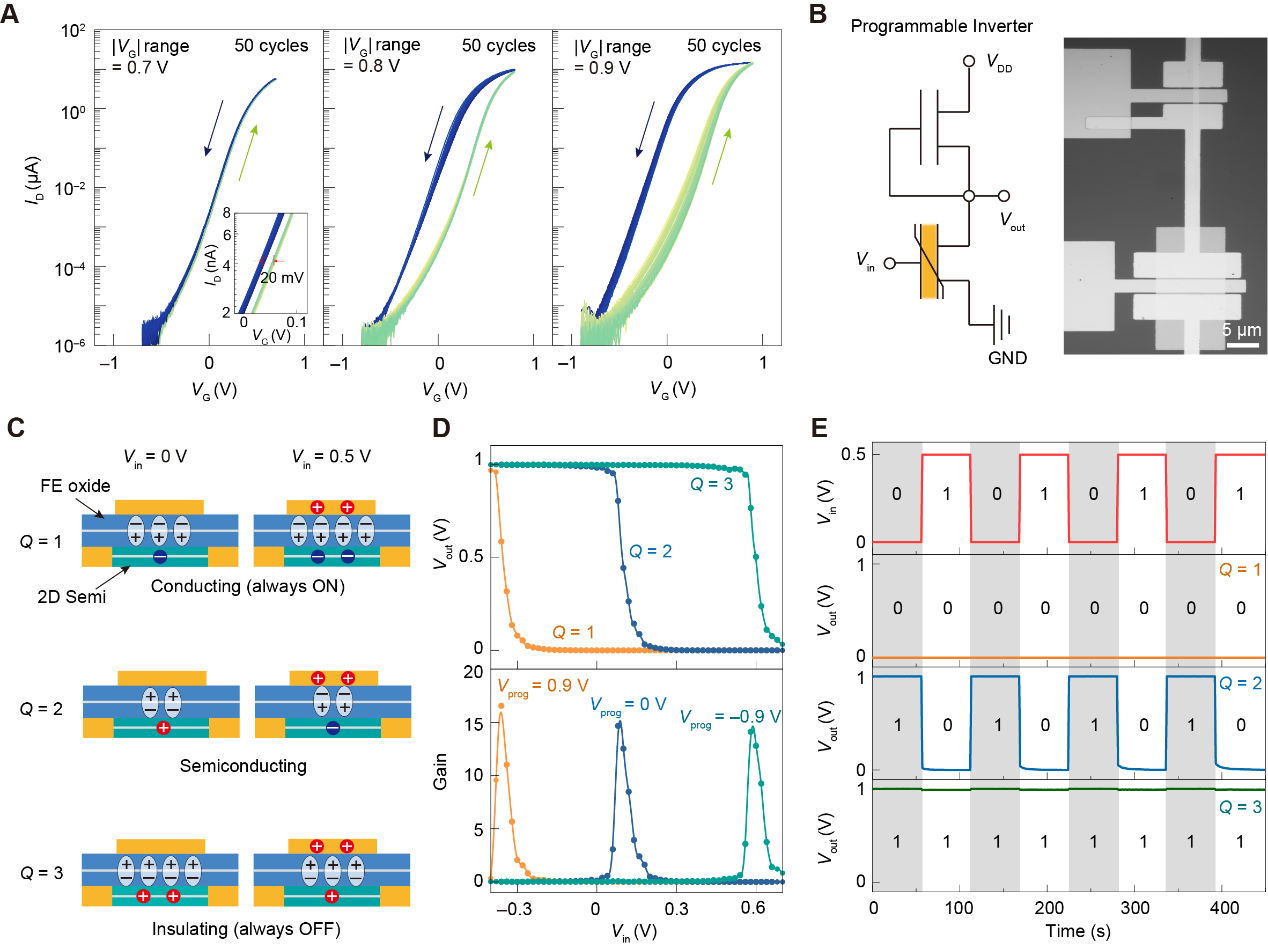

突破器件性能極限:超低工作電壓、高耐久的二維鐵電晶體管及電路

該研究工作進一步成功制備了高性能鐵電晶體管陣列(圖3)。該器件在0.8V超低電壓和20ns高速寫入條件下,實現了超過1.5×1012次的循環耐久性,同時具備超過10年的保持時間、5bit多級存儲態以及2.8 fJ bit−1μm−2的超低能耗,已超越同類型器件的工業最高水平,完全滿足云端AI計算對可靠性的嚴苛要求。這項工作突破了傳統鐵電材料在保持時間與耐久性、速度與能耗之間的性能制約,為面向AI計算需求的低功耗、三維集成存算一體架構提供了極具潛力的解決方案。進一步構建的可動態重構存內邏輯運算電路在CMOS常規低工作電壓(<1V)下即可實現“一器兩用”的可重構邏輯功能(圖4),充分展示了其在下一代存算一體架構中的重要應用潛力,為構建自適應、低功耗的智能計算系統奠定了關鍵器件基礎。

圖3. 二維α-Bi2SeO5/Bi2O2Se鐵電晶體管器件及性能

圖4. 低功耗二維α-Bi2SeO5/Bi2O2Se鐵電晶體管基可重構存內邏輯電路

審稿人評價認為:“該工作不僅突破了傳統鐵電材料的厚度極限與集成難題,也為鐵電二維電子學開辟了新路徑——Bi2SeO5鐵電層作為二維半導體Bi2O2Se的自然氧化物,具備天然的集成優勢。鐵電晶體管展現出優異的存儲性能和高度均一性,彰顯出顯著的應用潛力。”“這項工作將對鐵電材料和器件領域產生深遠影響,為鐵電二維電子學打開了大門。”

綜上所述,該研究在國際上首次實現了晶圓級超薄均勻的二維鐵電氧化物薄膜制備以及與二維半導體的三維異質集成,并研制了超低工作電壓與超高耐久性的鐵電晶體管及可重構存內邏輯電路。該研究同時突破了鐵電材料制備與鐵電器件性能極限,為下一代高性能、低功耗芯片技術提供了全新的材料平臺與集成方案,標志著“超越摩爾”路線實現了從材料創新到功能驗證的重要跨越。

該論文通訊作者為彭海琳及團隊的特聘副研究員劉洪濤,第一作者為北京大學化學與分子工程學院博雅博士后武欽慈,博士研究生李忠睿、韓秉辰、孫瑋玉、劉沁紜及薛騁遠。該工作合作者還包括北京大學物理學院高宇南研究員和賓夕法尼亞州立大學顏丙海教授等。該工作得到了國家自然科學基金委、科技部、新基石科學基金會等項目的資助,并得到了北京大學化學與分子工程學院分子材料與納米加工實驗室(MMNL)儀器平臺的支持。

所有評論僅代表網友意見,與本站立場無關。